## LED Driver ICs-General Application Note

Lauren Liu, Simon Wu April 03, 2007

#### **Foreword**

- PrecisionDrive<sup>™</sup> series provide outstanding performance. However, there are still conditions to use the driver correctly.

- This application note provides basic criteria for LED module designs. So, "general" is called.

- Following the guidelines, chip users (module designers) are able to generate not only feasible (workable) designs but also cost-effective (reliable) engineering solutions.

#### **Outline**

- 1. DC Operating Points

- 1.1 DC operating point

- 1.2 Minimum of V<sub>DS</sub>

- 1.3 Maximum of V<sub>DS</sub> under the limitation of heat dissipation

- 1.4 Maximum Power Dissipation

- ◆ 1.5 Cascade LEDs vs. Max. Power Dissipation

- 1.6 Solution to Minimizing Total VF Deviation

- ◆ 1.7 Example for a lighting solution (MBI1816)

- 1.8 Rext and Rtrim

- 2. Digital Signals

- 2.1 Digital Signals

- 2.2 Minimum Pulse Width of /OE

- 2.3 Signal Conditioning

- 2.4 Delay Matching

- ◆ 2.5 Logic Level

- 2.6 Buffer output capacity

#### 3. Switching noise and circuit Layout

- ◆ 3.1 Switching noise on V<sub>DD</sub>

- ♦ 3.2 Solution 1

- ♦ 3.3 Solution 2

- ♦ 3.4 Solution 3

- 3.5 Overshoot

- ◆ 3.6 Voltage Spike Damages Driver IC

- ◆ 3.7 Placement of Drivers on PCB

- 3.8 Placement of Drivers off PCB

- 3.9 Placement of Capacitors

- ◆ 3.10 Reducing the voltage drop in the long conduction line

- ◆ 3.11 Oscillation at OUT pins

- ◆ 3.12 Vrext oscillation

- ◆ 3.13 Power Supply's EMI Suppression

## 1. DC Operating Points

- 1.1 DC operating point

- 1.2 Minimum of V<sub>DS</sub>

- 1.3 Maximum of V<sub>DS</sub> under the limitation of heat dissipation

- 1.4 Maximum Power Dissipation

- 1.5 Cascade LEDs vs. Max. Power Dissipation

- 1.6 Solution to Minimizing Total VF Deviation

- 1.7 Example for a lighting solution (MBI1816)

- 1.8 Rext and Rtrim

## 1.1 DC Operating Point

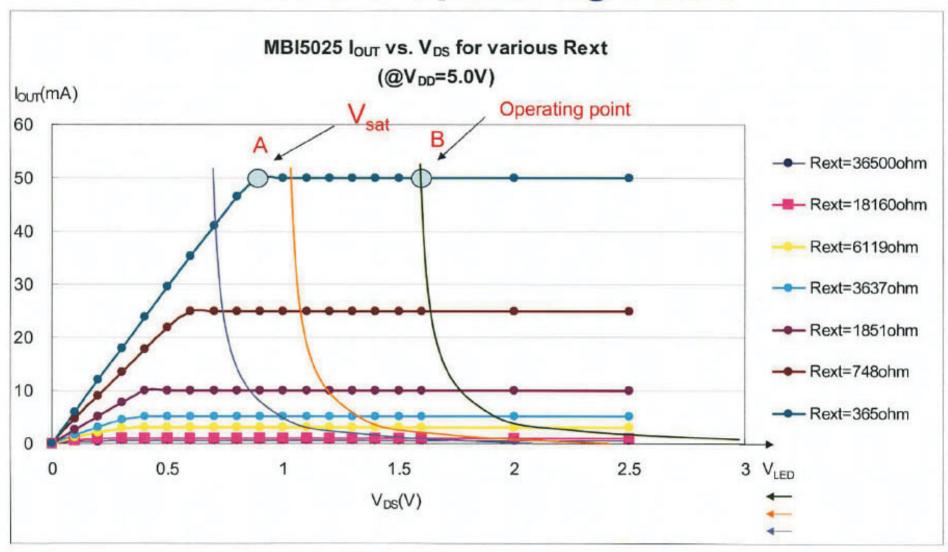

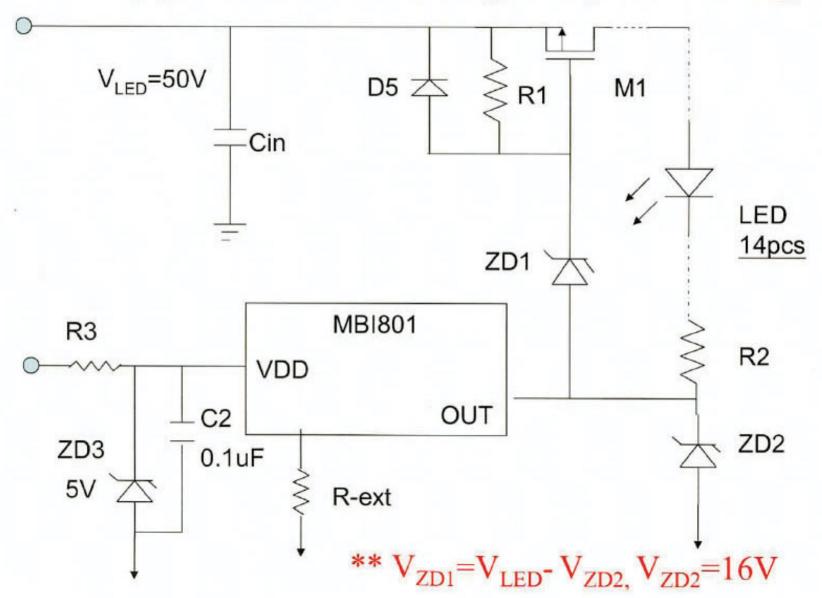

Fig. 1.

## 1.2 Minimum of V<sub>DS</sub>

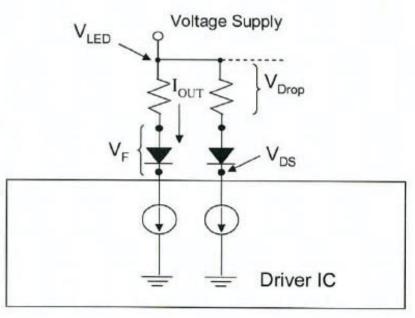

- Considerations of operating point, minimum of V<sub>DS</sub>

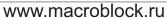

- ◆ Both V<sub>LED</sub> and V<sub>F</sub> determine V<sub>DS</sub>

- If V<sub>LED</sub> is too high, causing V<sub>DS</sub> being too high, this will lead to heating problem in driver ICs.

- $V_{DS} > V_{sat}$ , where  $V_{sat}$  is saturation point (i.e 0.7V@50mA)

- In order to keep constant current

- ♦  $V_{\rm DS} = V_{\rm LED}$   $V_{\rm F,max}$ - $V_{\rm DROP}$ > $V_{\rm sat}$ , where  $V_{\rm F}$  is LED forward voltage, and  $V_{\rm F,min}$  $\leq$  $V_{\rm F}$   $\leq$  $V_{\rm F,max}$  in LED's datasheet.

Fig. 2.

# 1.3 Maximum of V<sub>DS</sub> under the limitation of heat dissipation

- $\blacksquare$  Maximum of  $V_{DS}$  is limited by power dissipation

- $P_{\text{D(act)}} = V_{\text{DD}} \times I_{\text{DD}} + V_{\text{DS}} \times I_{\text{OUT}} \times N$ , where N is LED channel numbers.

Lower voltage of  $V_{\rm DS}$  can obtain lower power dissipation. Therefore, DC operating point slightly larger and approaching the saturation point is better.

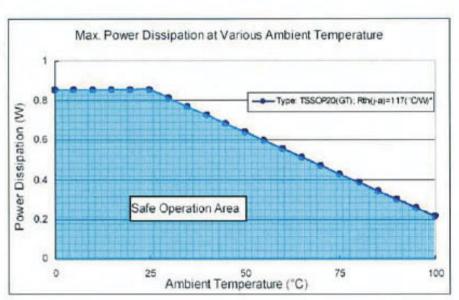

## 1.4 Maximum Power Dissipation

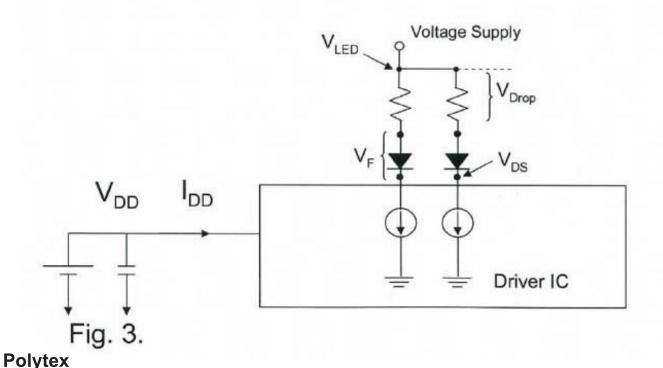

Fig. 4.

When the driver ICs are operated at more than 80°C,

P<sub>D</sub> should be <1.5W for GD type to keep ICs in the safe operation area.

Po should be <1.0W for GF type to keep ICs in the safe operation area.

P<sub>D</sub> should be <0.8W for CP type to keep ICs in the safe operation area.

#### 1.5 Cascade LEDs vs. Max. Power Dissipation

| MBI1816 Calculation                                                                    | RED LED for Lighting |        |      |

|----------------------------------------------------------------------------------------|----------------------|--------|------|

| Conditions                                                                             | 1                    | 2      |      |

| V <sub>LED</sub> (Applied Voltage)                                                     | 17                   | 17     | V    |

|                                                                                        | VF-max               | VF-min |      |

| V <sub>F</sub> ( LED)                                                                  | 2                    | 1.8    | V    |

| LED Current<br>/ per string                                                            | 0.04                 | 0.04   | A    |

| LED Series numbers<br>/ per string                                                     | 8                    | 8      | pcs  |

| IC's Output pin voltage( Vds) @ 40mA/Channel Suggest 0.7V at least@ 40mA / per channel | 0.70                 | 2.30   | v    |

| Series resistor<br>between V <sub>LED</sub> and LED                                    | 7.50                 | 7.50   | Ohm  |

| Pd on series resistor                                                                  | 0.01                 | 0.01   | Watt |

| Total IC's Pd@40mA<br>/ per channel                                                    | 0.448                | 1.472  | Watt |

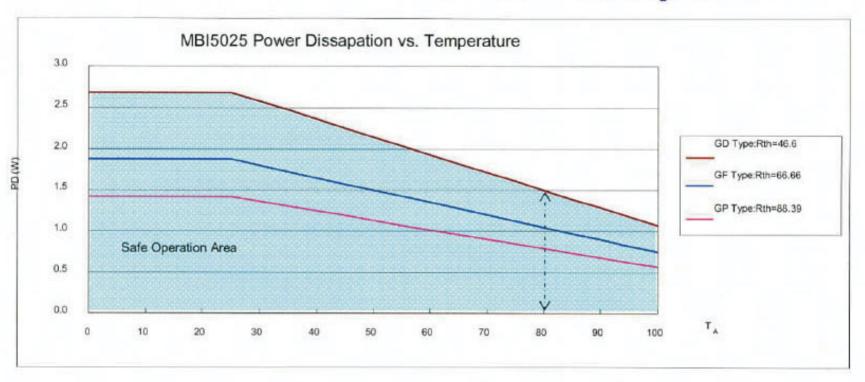

The tolerance of V<sub>F</sub> will probably lead to driver IC over heating

## 1.6 Solution to Minimizing Total VF Deviation

11

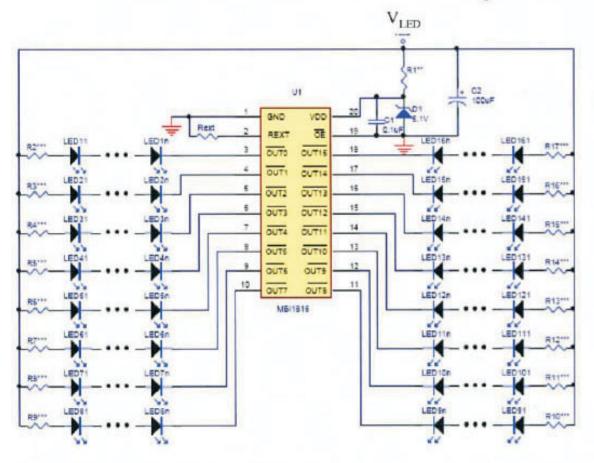

# 1.7 Example for a Lighting Solution (MBI1816)

Fig. 6

<sup>&#</sup>x27; V<sub>LED</sub> > V<sub>DS</sub> + V<sub>F,LED</sub> x n; V<sub>F,LED</sub>: Forward voltage of LED; n: LED count

<sup>\*\*</sup> R1 = (V<sub>LED</sub> - 5.1V) / I<sub>DD</sub>; refer to Electrical Characteristics for I<sub>DD</sub>

<sup>&</sup>quot;\*\* R2~R17 =  $[V_{LED} - V_{DS} - (V_{F,LED} \times n)] / I_{LED}$

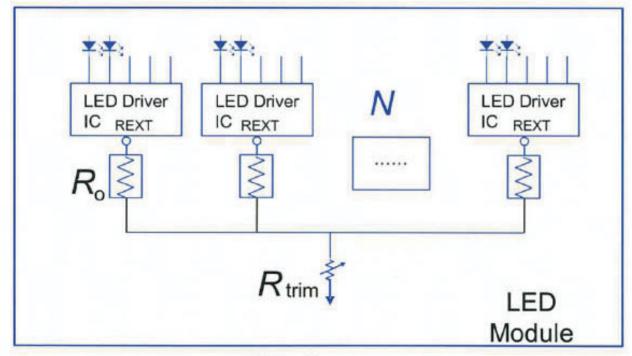

#### 1.8 Rext and Rtrim

#### Setting Output Current in a Group

- $\blacksquare$   $R_{\text{trim}}$  and  $R_{\text{ext}}$

- $ightharpoonup R_{\text{ext}} = R_{\text{o}} + N_X R_{\text{trim}}$ , where N is IC number.

Fig. 7

Constraint: N\*R<sub>trim</sub><R<sub>o</sub>/3; otherwise, the chip skew will be not good.

#### 2. Digital Signals

- 2.1 Digital Signals

- 2.2 Minimum Pulse Width of /OE

- 2.3 Signal Conditioning

- 2.4 Delay Matching

- 2.5 Logic Level

- 2.6 Buffer output capacity

## 2.1 Digital Signals

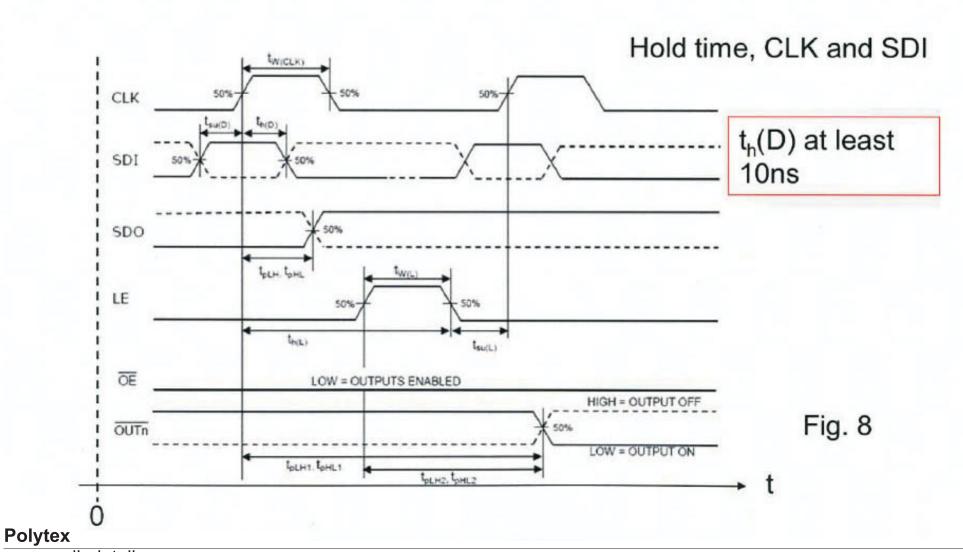

#### 2.2 Minimum Pulse Width of /OE

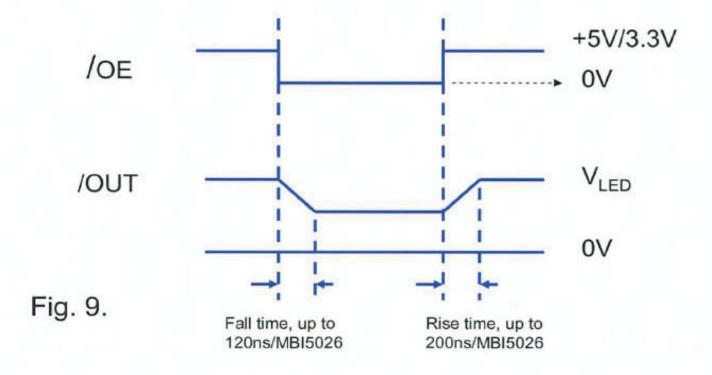

■ The relationship between /OE and /OUT

If /OE pulse width is less than 320 ns, the effective output pulse width will be distorted. Additional compensation to PWM will be necessary.

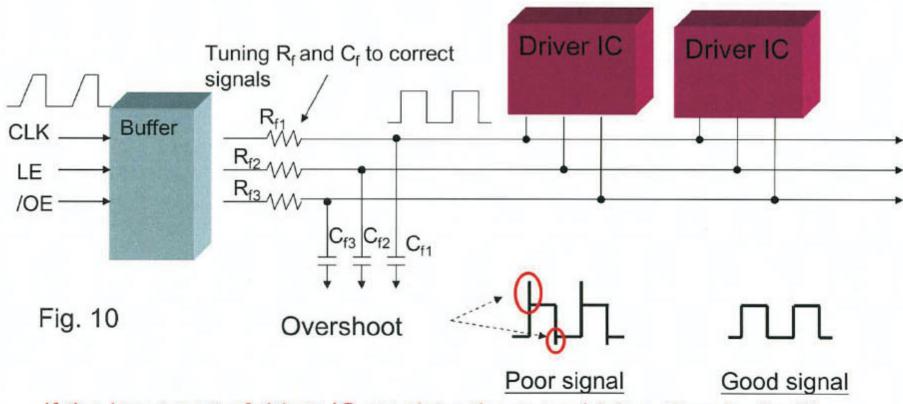

#### 2.3 Signal Conditioning

#### Check digital signals, CLK, LE, and /OE

If the input port of driver IC receives the over driving signals, it will be probably damaged by the signals, which will then increase the IC temperature.

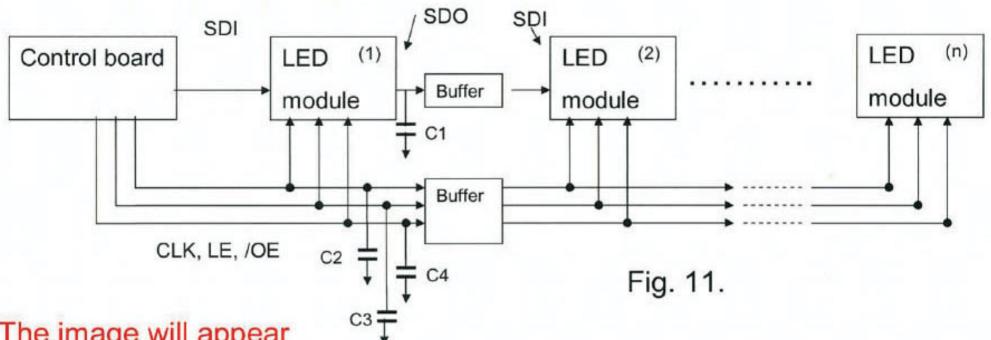

## 2.4 Delay Matching

The image will appear abnormal, if the logic signal does not occur in the right timing. SDI vs. CLK is especially critical.

By adjusting C1~C4, the signals of SDI, CLK, LE and /OE may follow the exact timing shown as Fig. 6.

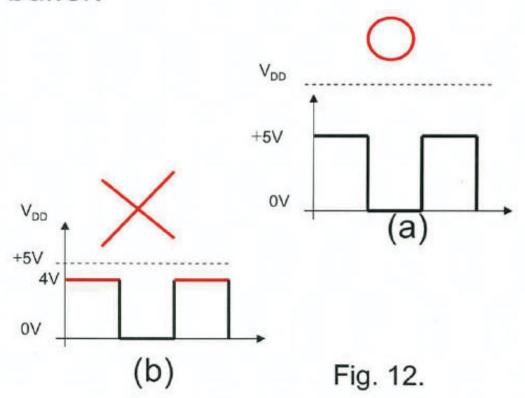

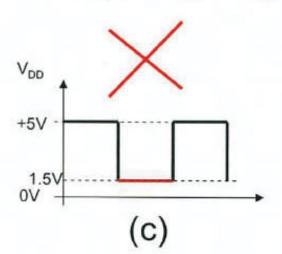

#### 2.5 Logic Level

- The necessary voltage levels to transmit valid logic 1 and logic 0 are: V<sub>IH</sub> > 0.8xV<sub>DD</sub>, and V<sub>IL</sub> < 0.3xV<sub>DD</sub>

- ightharpoonup When  $V_{DD}$  =5V,  $V_{IH}$  = 4.0V and  $V_{IL}$  < 1.5V

- 74HCxxx buffer will be required, rather than 74LSxxx buffer.

The image will appear abnormal, if the logic level does not transmit in the right voltage range.

## 2.6 Buffer Output Capacity

- In general, the LED display board will need signal buffer to driver LED driver. Further, one signal buffer will driver several LED drivers in a LED display board. A reference equation to calculate the number of LED drivers connecting to buffer's output port, it is shown as following. Assume that Vdd is 5V for buffer.

- N<sub>1</sub>=I<sub>source,buffer</sub>/(Vdd/250K), N<sub>2</sub>=I<sub>sink,buffer</sub>/(Vdd/250K), The two numbers, N<sub>1</sub> and N<sub>2</sub>, the smaller one is the number of LED drivers connecting to buffer's output port.

- Where I<sub>source,buffer</sub> is the minimum source current shown in buffer's datasheet, and I<sub>sink,buffer</sub> is the minimum sink current shown in buffer's datasheet.

## 3. Switching Noise and Circuit Layout

- 3.1 Switching noise on V<sub>DD</sub>

- 3.2 Solution 1

- 3.3 Solution 2

- 3.4 Solution 3

- 3.5 Overshoot

- 3.6 Voltage Spike Damages Driver IC

- 3.7 Placement of Drivers on PCB

- 3.8 Placement of Drivers off PCB

- 3.9 Placement of Capacitors

- 3.10 Solving voltage drop with paralleling wires connector

- 3.11 Oscillation at OUT pins

- 3.12 Vrext oscillation

- 3.13 Power Supply's EMI Suppression

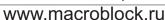

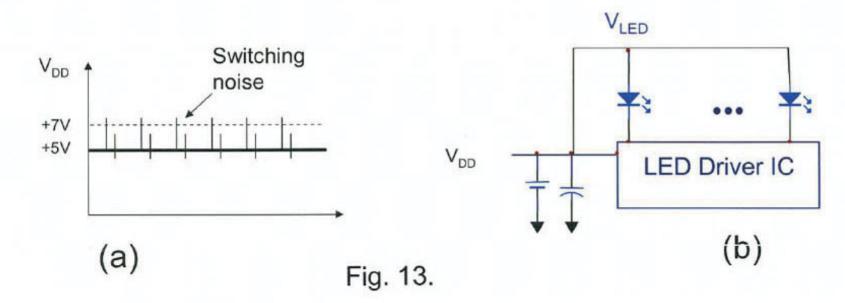

## 3.1 Switching Noise on V<sub>DD</sub>

- When V<sub>DD</sub> is disturbed by a high-frequency noise, the driver IC might malfunction

- If V<sub>DD</sub> and V<sub>LED</sub> are connected to the same supply voltage source, as shown in Fig. 11(b), V<sub>DD</sub> will be very noisy.

- ◆ The temperature on the driver IC will increase and cause the damage of driver IC.

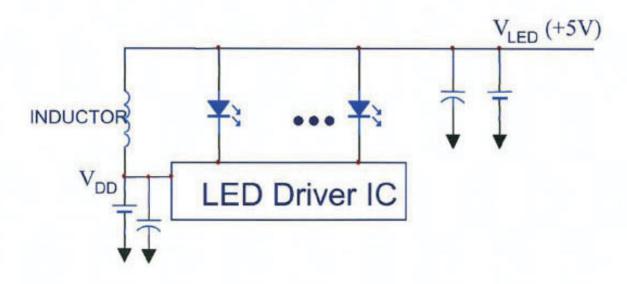

#### 3.2 Solution 1

- To separate V<sub>DD</sub> from V<sub>LED</sub>,

- Even though they are the same voltage level

#### 3.3 Solution 2

- To add an inductor in series between V<sub>DD</sub> and V<sub>LED</sub>, in case there is only one voltage source

- To add two capacitors for V<sub>DD</sub> and V<sub>LED</sub> individually

#### Case Study

Fig. 15.

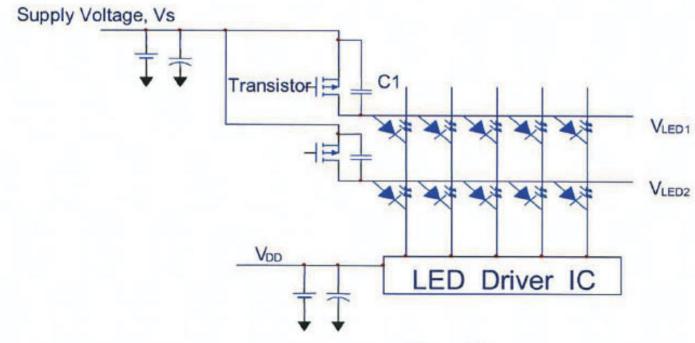

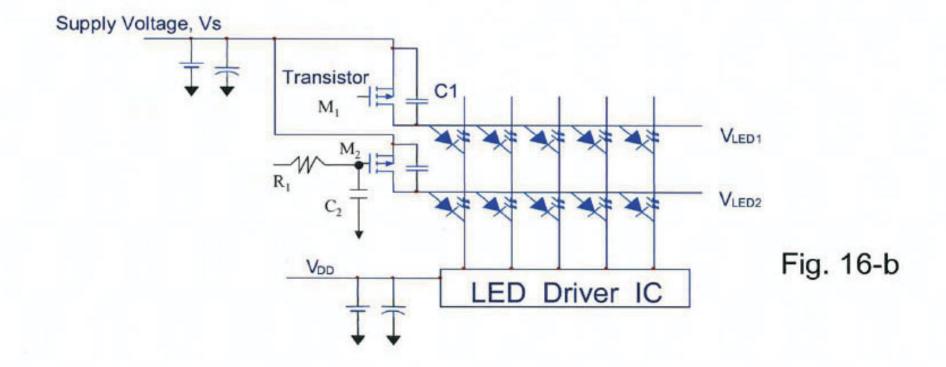

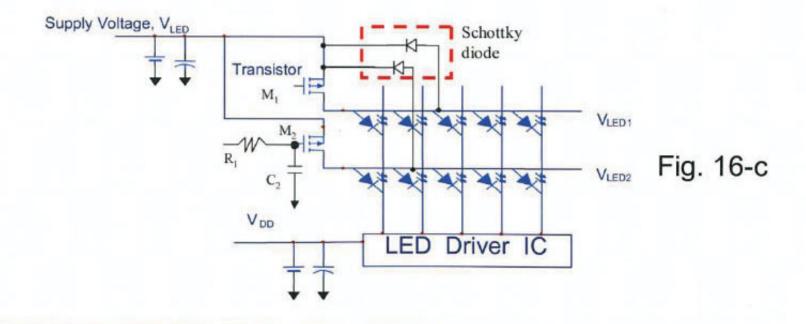

#### 3.4 Solution 3

To add a capacitor (C1) beside the transistor in parallel in time-multiplexing application (dynamic/ scan type)

Fig. 16-a.

To add a capacitor (C<sub>2</sub>) across Gate and Gnd or to add resistor R<sub>1</sub> in series with Gate terminal in order to reduce the switching speed of MOSFET.

If the switching noise was caused by fast rising time of driver IC, provide the release loop for magnetic energy in parasitic inductor by adding Schottky diodes from the V<sub>LED1,2</sub> To V<sub>LED.</sub>

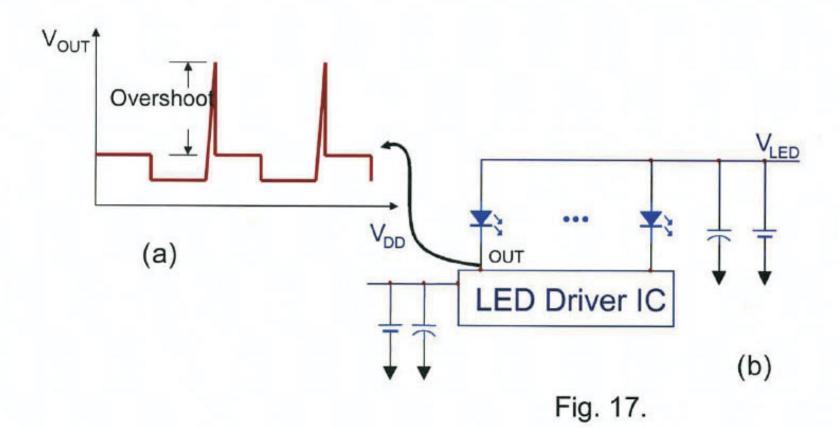

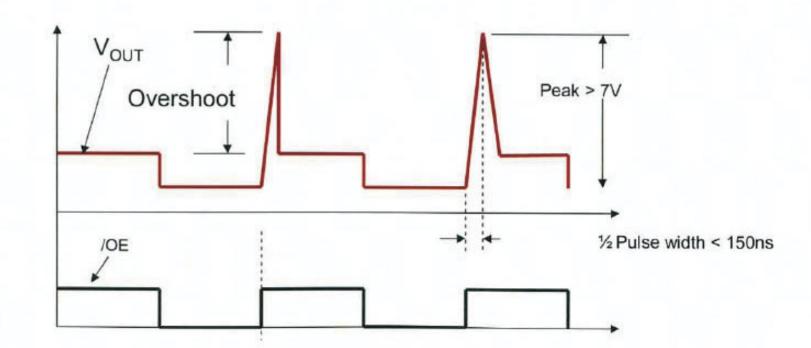

#### 3.5 Overshoot

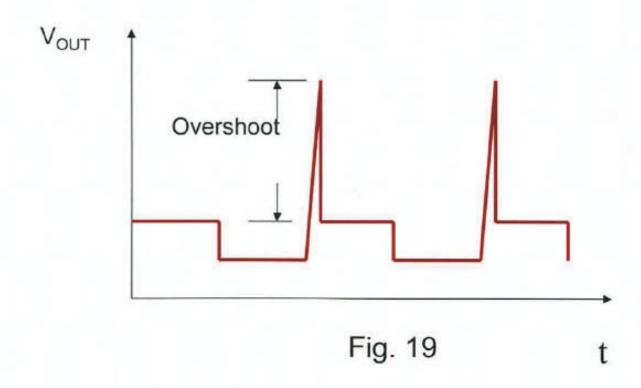

■ What is voltage overshoot at OUT pin?

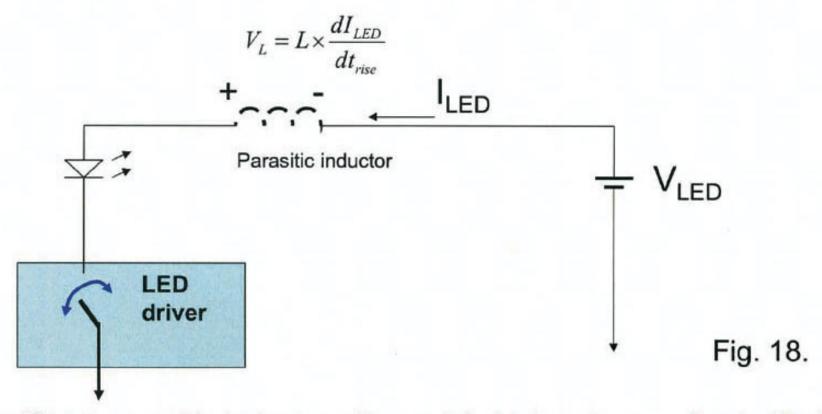

#### How does the overshoot come?

A significant parasitic inductor will result in high voltage spike in /OUT pins. Shorter conduction line will have smaller parasitic inductor.

- The overshoot will probably damage IC's /OUT pins if the voltage spike has enough energy.

- In addition, if V<sub>DD</sub> is not separated from V<sub>LED</sub>, V<sub>DD</sub> may be affected by the voltage spike.

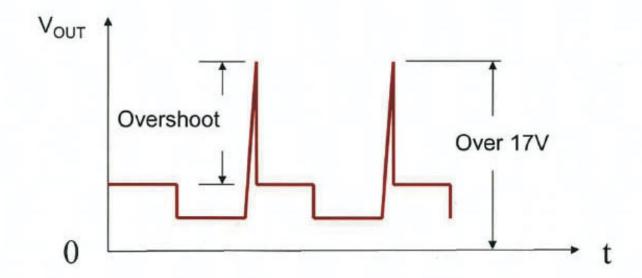

## 3.6 Voltage Spike Damages Driver IC

- Two conditions of voltage spike that damages driver IC.

- Condition 1: The peak of the voltage spike is over 17V.

Fig. 20

**Polytex**

- Condition 2: When the voltage spike is under 17V while ½ pulse width of the voltage spike is smaller than the delay time between /OE and /OUT, the voltage spike will damage the driver IC.

- For example, per MBI5026 datasheet, the voltage spike of output pin is 7V and the ½ pulse width is smaller than 150ns.

Fig. 21.

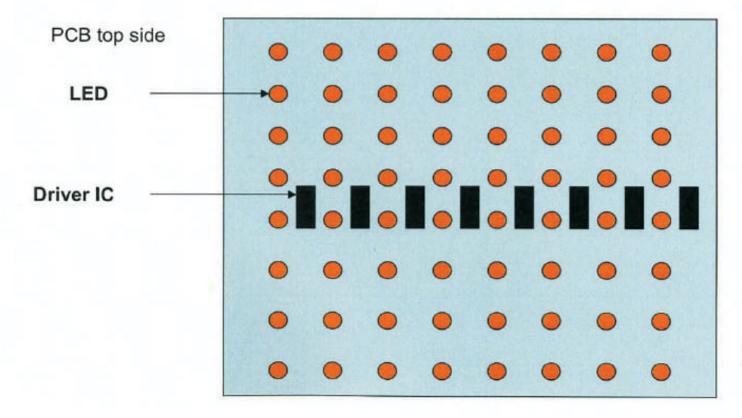

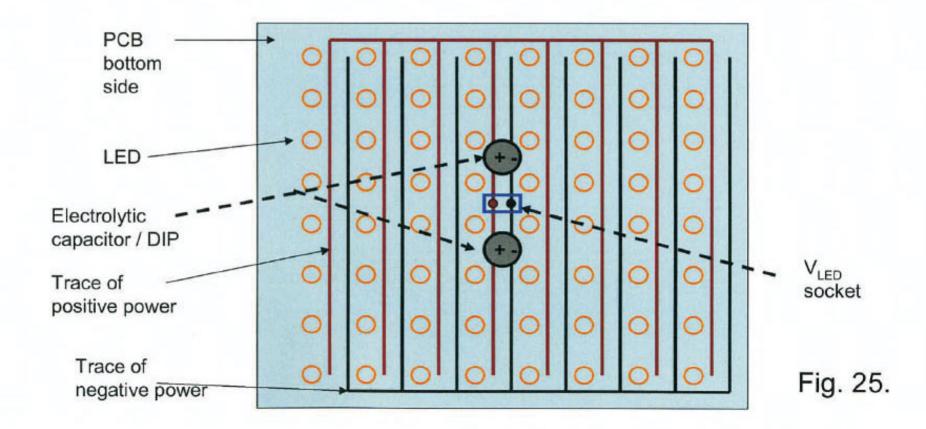

#### 3.7 Placement of Drivers on PCB

The Driver IC should be geographically as close to the LED as possible.

Fig. 22.

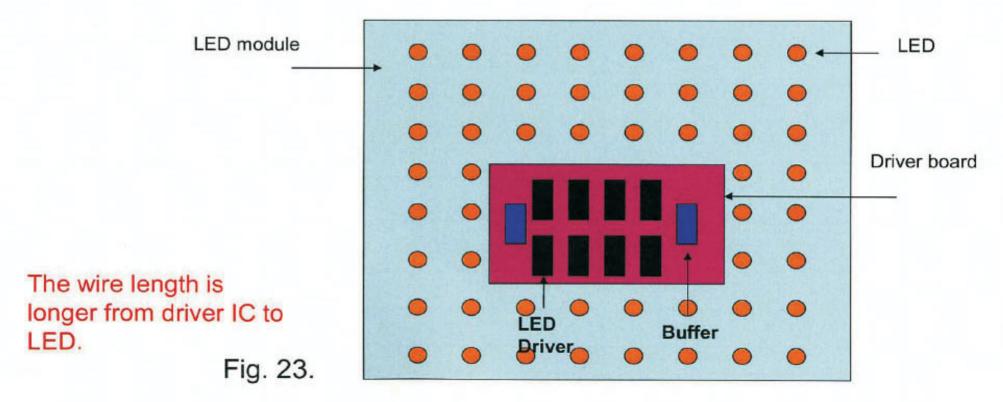

#### 3.8 Placement of Drivers off PCB

- In some cases, the driver ICs are placed on another driver board and the driver board is connected to an LED module.

- For LED modules with wide pitches, 30 mm, the wire is long, from driver IC to LED.

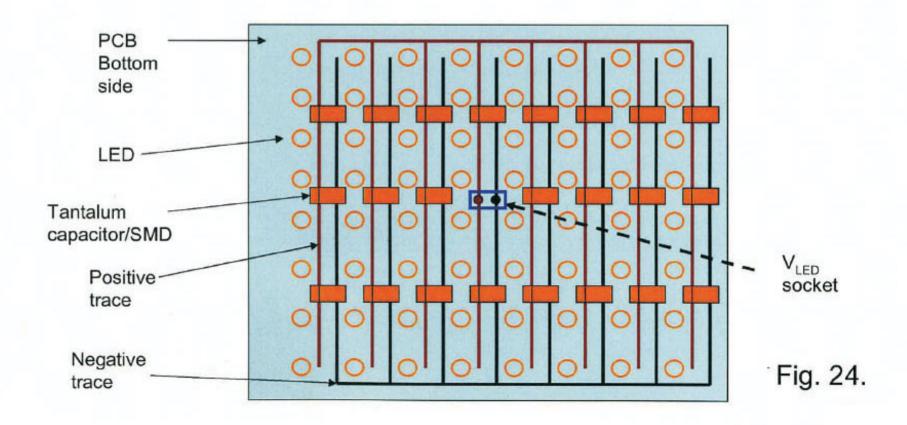

## 3.9 Placement of Capacitors

■ Distributed capacitors for V<sub>LED</sub>

## **Placement of Capacitors**

Poor arrangement regarding capacitors for V<sub>LED</sub>

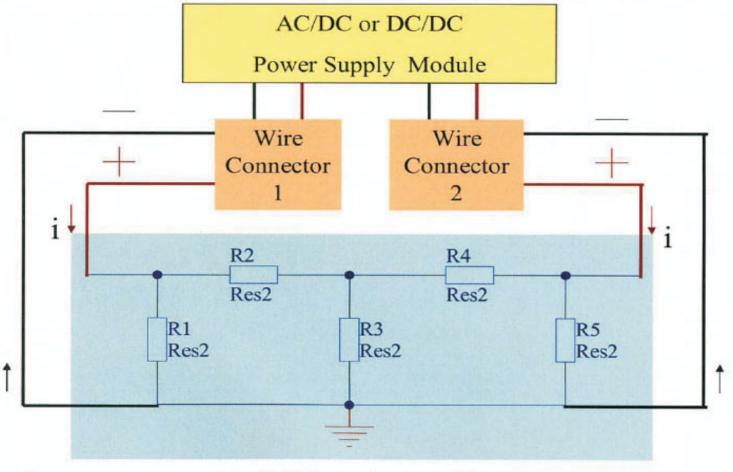

## 3.10 Reducing The Voltage Drop in The Long Conduction Line

Fig. 26

If a voltage source are not on PCB's center, provide power source on two terminals to reduce voltage drop on long conduction line.

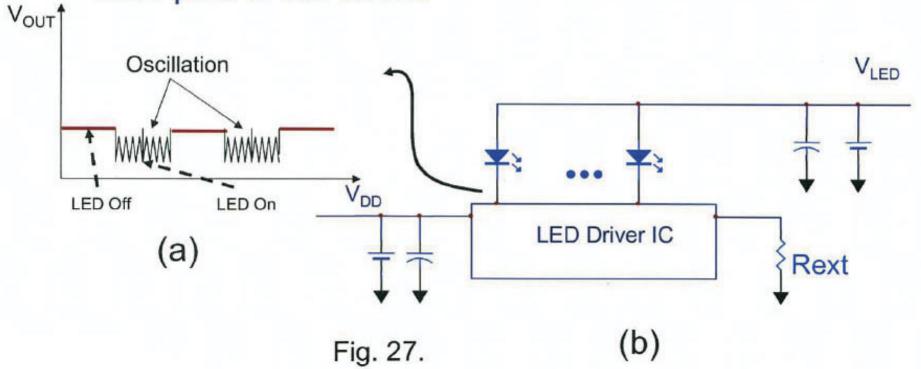

## 3.11 Oscillation at OUT pins

- The oscillation occurs usually with a poor phase margin inside the driver.

- The phase margin is also contributed by the parasitic inductance of the LED wires from the LED anodes to OUT pins of the driver.

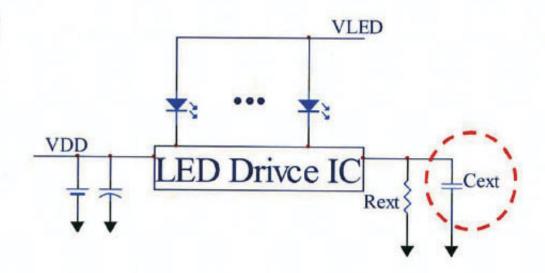

#### 3.12 Vrext Oscillation

- The ill grounding of Rext will also has risks in output oscillation.

- Method to avoid oscillation in output port

- ◆ Add Cext ≤ 47nF in shunt with pin Rext

Fig. 28.

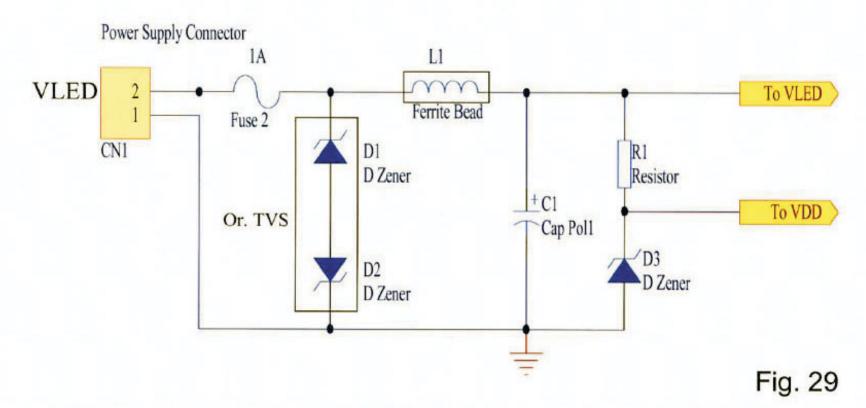

## 3.13 Power Supply's EMI Suppression

D1+D2: Total claim voltage =VLED +2V is recommended, or Bi-direction TVS component

Ferrite Bead: NiZn ferrite material is recommended

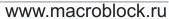

## **Applications of High Input Voltage-I**

## **Applications of High Input Voltage-II**

When output channels are turned off, most of supply voltage (VLED) will drop on VR.

Shunts a Mega Ohm resistance at output pin terminals to prevent LED from low Vf due to slight brightness.